# Test Resource Partitioning for System-on-a-Chip

Krishnendu Chakrabarty Vikram Iyengar Anshuman Chandra

Kluwer Academic Publishers

# **Test Resource Partitioning For Systemonachip**

Dimitris Gizopoulos,A.

Paschalis,Yervant Zorian

## **Test Resource Partitioning For Systemonachip:**

Test Resource Partitioning for System-on-a-Chip Krishnendu Chakrabarty, Vikram Iyengar, Anshuman Chandra, 2002-06-30 Test Resource Partitioning for System on a Chip is about test resource partitioning and optimization techniques for plug and play system on a chip SOC test automation Plug and play refers to the paradigm in which core to core interfaces as well as core to SOC logic interfaces are standardized such that cores can be easily plugged into virtual sockets on the SOC design and core tests can be plugged into the SOC during test without substantial effort on the part of the system integrator The goal of the book is to position test resource partitioning in the context of SOC test automation as well as to generate interest and motivate research on this important topic SOC integrated circuits composed of embedded cores are now commonplace Nevertheless There remain several roadblocks to rapid and efficient system integration Test development is seen as a major bottleneck in SOC design and test challenges are a major contributor to the widening gap between design capability and manufacturing capacity Testing SOCs is especially challenging in the absence of standardized test structures test automation tools and test protocols Test Resource Partitioning for System on a Chip responds to a pressing need for a structured methodology for SOC test automation It presents new techniques for the partitioning and optimization of the three major SOC test resources test hardware testing time and test data volume Test Resource Partitioning for System on a Chip paves the way for a powerful integrated framework to automate the test flow for a large number of cores in an SOC in a plug and play fashion The framework presented allows the system integrator to reduce test cost and meet short time to market requirements **Test Resource Partitioning for System-on-a-Chip** Vikram Iyengar, Anshuman Chandra, 2012-12-06 Test Resource Partitioning for System on a Chip is about test resource partitioning and optimization techniques for plug and play system on a chip SOC test automation Plug and play refers to the paradigm in which core to core interfaces as well as core to SOC logic interfaces are standardized such that cores can be easily plugged into virtual sockets on the SOC design and core tests can be plugged into the SOC during test without substantial effort on the part of the system integrator The goal of the book is to position test resource partitioning in the context of SOC test automation as well as to generate interest and motivate research on this important topic SOC integrated circuits composed of embedded cores are now commonplace Nevertheless There remain several roadblocks to rapid and efficient system integration Test development is seen as a major bottleneck in SOC design and test challenges are a major contributor to the widening gap between design capability and manufacturing capacity Testing SOCs is especially challenging in the absence of standardized test structures test automation tools and test protocols Test Resource Partitioning for System on a Chip responds to a pressing need for a structured methodology for SOC test automation It presents new techniques for the partitioning and optimization of the three major SOC test resources test hardware testing time and test data volume Test Resource Partitioning for System on a Chip paves the way for a powerful integrated framework to automate the test flow for a large number of cores in an SOC in a plug and

play fashion The framework presented allows the system integrator to reduce test cost and meet short time to market requirements SOC (System-on-a-Chip) Testing for Plug and Play Test Automation Krishnendu Chakrabarty,2013-04-17 System on a Chip SOC integrated circuits composed of embedded cores are now commonplace Nevertheless there remain several roadblocks to rapid and efficient system integration Test development is seen as a major bottleneck in SOC design and manufacturing capabilities Testing SOCs is especially challenging in the absence of standardized test structures test automation tools and test protocols In addition long interconnects high density and high speed designs lead to new types of faults involving crosstalk and signal integrity SOC System on a Chip Testing for Plug and Play Test Automation is an edited work containing thirteen contributions that address various aspects of SOC testing SOC System on a Chip Testing for Plug and Play Test Automation is a valuable reference for researchers and students interested in various aspects of SOC testing

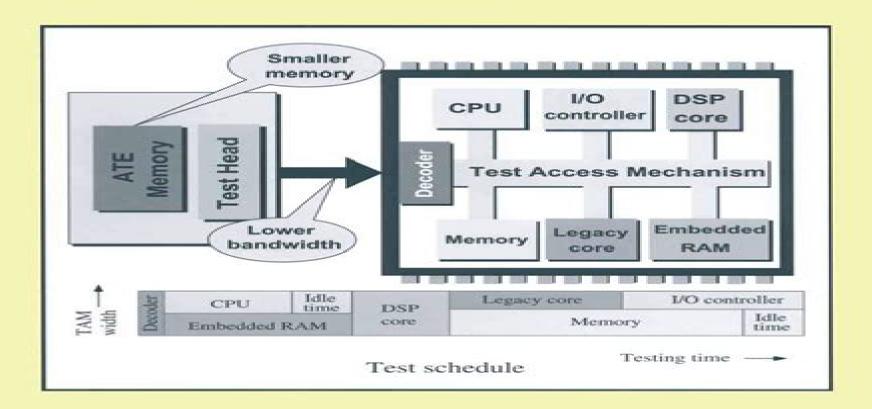

System-on-Chip Bashir M. Al-Hashimi,2006-01-31 This book highlights both the key achievements of electronic systems design targeting SoC implementation style and the future challenges presented by the continuing scaling of CMOS technology Introduction to Advanced System-on-Chip Test Design and Optimization Erik Larsson,2006-03-30 SOC test design and its optimization is the topic of Introduction to Advanced System on Chip Test Design and Optimization It gives an introduction to testing describes the problems related to SOC testing discusses the modeling granularity and the implementation into EDA electronic design automation tools The book is divided into three sections i test concepts ii SOC design for test and iii SOC test applications The first part covers an introduction into test problems including faults fault types design flow design for test techniques such as scan testing and Boundary Scan The second part of the book discusses SOC related problems such as system modeling test conflicts power consumption test access mechanism design test scheduling and defect oriented scheduling Finally the third part focuses on SOC applications such as integrated test scheduling and TAM design defect oriented scheduling and integrating test design with the core selection process

Advances in VLSI and Embedded Systems Zuber Patel, Shilpi Gupta, Nithin Kumar Y. B., 2020-08-28 This book presents select peer reviewed proceedings of the International Conference on Advances in VLSI and Embedded Systems AVES 2019 held at SVNIT Surat Gujarat India The book covers cutting edge original research in VLSI design devices and emerging technologies embedded systems and CAD for VLSI With an aim to address the demand for complex and high functionality systems as well as portable consumer electronics the contents focus on basic concepts of circuit and systems design fabrication testing and standardization This book can be useful for students researchers as well as industry professionals interested in emerging trends in VLSI and embedded systems

System-Level Validation Mingsong Chen, Xiaoke

Qin, Heon-Mo Koo, Prabhat Mishra, 2012-09-19 This book covers state of the art techniques for high level modeling and validation of complex hardware software systems including those with multicore architectures Readers will learn to avoid time consuming and error prone validation from the comprehensive coverage of system level validation including high level

modeling of designs and faults automated generation of directed tests and efficient validation methodology using directed tests and assertions The methodologies described in this book will help designers to improve the quality of their validation performing as much validation as possible in the early stages of the design while reducing the overall validation effort and Design and Test Technology for Dependable Systems-on-Chip Ubar, Raimund, Raik, Jaan, Vierhaus, Heinrich cost Theodor, 2010-12-31 This book covers aspects of system design and efficient modelling and also introduces various fault models and fault mechanisms associated with digital circuits integrated into System on Chip SoC Multi Processor System on Chip MPSoC or Network on Chip NoC VLSI-SoC: Advanced Topics on Systems on a Chip Ricardo Reis, Vincent Mooney, Paul Hasler, 2009-04-05 This book contains extended and revised versions of the best papers that were presented during the fifteenth edition of the IFIP IEEE WG10 5 International Conference on Very Large Scale Integration a global System on a Chip Design CAD conference The 15th conference was held at the Georgia Institute of Technology Atlanta USA October 15 17 2007 Previous conferences have taken place in Edinburgh Trondheim Vancouver Munich Grenoble Tokyo Gramado Lisbon Montpellier Darmstadt Perth and Nice The purpose of this conference sponsored by IFIP TC 10 Working Group 10 5 and by the IEEE Council on Electronic Design Automation CEDA is to provide a forum to exchange ideas and show industrial and academic research results in the field of microelectronics design The current trend toward increasing chip integration and technology process advancements brings about stimulating new challenges both at the physical and system design levels as well in the test of these systems VLSI SoC conferences aim to address these exciting new issues

Power-Aware Testing and Test Strategies for Low Power Devices Patrick Girard, Nicola Nicolici, Xiaoging Wen, 2010-03-11 Managing the power consumption of circuits and systems is now considered one of the most important challenges for the semiconductor industry Elaborate power management strategies such as dynamic voltage scaling clock gating or power gating techniques are used today to control the power dissipation during functional operation The usage of these strategies has various implications on manufacturing test and power aware test is therefore increasingly becoming a major consideration during design for test and test preparation for low power devices This book explores existing solutions for power aware test and design for test of conventional circuits and systems and surveys test strategies and EDA solutions for testing low power devices Production Testing of RF and System-on-a-chip Devices for Wireless Communications Keith B. Schaub, Joe Kelly, 2004 Technological advances have created a need for the merger and rethinking of past testing approaches for wireless equipment This first of its kind resource offers professionals an in depth overview of cutting edge RF radio frequency and SOC system on a chip product testing for wireless communications System-on-Chip Test Architectures Laung-Terng Wang, Charles E. Stroud, Nur A. Touba, 2010-07-28 Modern electronics testing has a legacy of more than 40 years The introduction of new technologies especially nanometer technologies with 90nm or smaller geometry has allowed the semiconductor industry to keep pace with the increased performance capacity demands from consumers As a result semiconductor test costs have been growing steadily and typically amount to 40% of today s overall product cost This book is a comprehensive guide to new VLSI Testing and Design for Testability techniques that will allow students researchers DFT practitioners and VLSI designers to master quickly System on Chip Test architectures for test debug and diagnosis of digital memory and analog mixed signal designs Emphasizes VLSI Test principles and Design for Testability architectures with numerous illustrations examples Most up to date coverage available including Fault Tolerance Low Power Testing Defect and Error Tolerance Network on Chip NOC Testing Software Based Self Testing FPGA Testing MEMS Testing and System In Package SIP Testing which are not yet available in any testing book Covers the entire spectrum of VLSI testing and DFT architectures from digital and analog to memory circuits and fault diagnosis and self repair from digital to memory circuits Discusses future nanotechnology test trends and challenges facing the nanometer design era promising nanotechnology test techniques including Quantum Dots Cellular Automata Carbon Nanotubes and Hybrid Semiconductor Nanowire Molecular Computing Practical problems at the end of each chapter for students Embedded Processor-Based Self-Test Dimitris Gizopoulos, A. Paschalis, Yervant Zorian, 2013-03-09 Embedded Processor Based Self Test is a guide to self testing strategies for embedded processors Embedded processors are regularly used today in most System on Chips SoCs Testing of microprocessors and embedded processors has always been a challenge because most traditional testing techniques fail when applied to them This is due to the complex sequential structure of processor architectures which consists of high performance datapath units and sophisticated control logic for performance optimization Structured Design for Testability DfT and hardware based self testing techniques which usually have a non trivial impact on a circuit s performance size and power can not be applied without serious consideration and careful incorporation into the processor design Embedded Processor Based Self Test shows how the powerful embedded functionality that processors offer can be utilized as a self testing resource Through a discussion of different strategies the book emphasizes on the emerging area of Software Based Self Testing SBST SBST is based on the idea of execution of embedded software programs to perform self testing of the processor itself and its surrounding blocks in the SoC SBST is a low cost strategy in terms of overhead area speed power development effort and test application cost as it is applied using low cost low speed test equipment Embedded Processor Based Self Test can be used by designers DfT engineers test practitioners researchers and students working on digital testing and in particular processor and SoC test This book sets the framework for comparisons among different SBST methodologies by discussing key requirements It presents successful applications of SBST to a number of embedded processors of different complexities and instruction set architectures **Urban Intelligence and Applications** Xiaohui Yuan, Mohamed Elhoseny, 2020-06-25 This volume presents selected papers from the International Conference on Urban Intelligence and Applications ICUIA which took place on May 10 12 2019 in Wuhan China The goal of the conference was to bring together researchers industry leaders policy makers and administrators to discuss emerging technologies and their

applications to advance the design and implementation of intelligent utilization and management of urban assets and thus contributing to the autonomous reliable and efficient operation of modern smart cities. The papers are collated to address major themes of urban sustainability urban infrastructure and management smart city applications image and signal processing natural language processing and machine learning for monitoring and communications applications The book will be of interest to researchers and industrial practitioners working on geospatial theories and tools smart city applications urban mobility and transportation and community well being and management **Fault Injection Techniques and Tools** for Embedded Systems Reliability Evaluation Alfredo Benso, Paolo Prinetto, 2005-12-15 Fault Injection Techniques and Tools for Embedded Systems Reliability Evaluation intends to be a comprehensive guide to Fault Injection techniques used to evaluate the dependability of a digital system The description and the critical analysis of different Fault Injection techniques and tools will be authored by key scientists in the field of system dependability and fault tolerance Wrapper Handbook Francisco da Silva, Teresa McLaurin, Tom Waayers, 2006-09-15 In the early to mid 1990 s while working at what was then Motorola Se conductor business changes forced my multi hundred dollar microprocessor to become a tens of dollars embedded core I ran into first hand the problem of trying to deliver what used to be a whole chip with something on the order of over 400 interconnect signals to a design team that was going to stuff it into a package with less than 220 signal pins and surround it with other logic I also ran into the problem of delivering microprocessor specification verifition a microprocessor is not just about the functions and instructions included with the instruction set but also the MIPs rating at some given f quency I faced two dilemmas one I could not deliver functional vectors without significant development of off core logic to deal with the reduced chip I O map and everybody s I O map was going to be a little different and two the JTAG 1149 1 boundary scan ring that was around my core when it was a chip was going to be woefully inadequate since it did not support speed signal application and capture and independent use separate from my core I considered the problem at length and came up with my own solution that was predominantly a separate non ITAG scan test wrapper that supported at speed application of launch capture cycles using the system clock But my problems weren t over at that point either

Oscillation-Based Test in Mixed-Signal Circuits Gloria Huertas Sánchez, Diego Vázquez García de la Vega, Adoración Rueda Rueda, Jose Luis Huertas Díaz, 2007-06-03 Oscillation Based Test in Mixed Signal Circuits presents the development and experimental validation of the structural test strategy called Oscillation Based Test OBT in short The results here presented allow to assert not only from a theoretical point of view but also based on a wide experimental support that OBT is an efficient defect oriented test solution complementing the existing functional test techniques for mixed signal circuits

<u>Testing Static Random Access Memories</u> Said Hamdioui,2013-06-29 Testing Static Random Access Memories covers testing of one of the important semiconductor memories types it addresses testing of static random access memories SRAMs both single port and multi port It contributes to the technical acknowledge needed by those involved in memory testing

engineers and researchers The book begins with outlining the most popular SRAMs architectures Then the description of realistic fault models based on defect injection and SPICE simulation are introduced Thereafter high quality and low cost test patterns as well as test strategies for single port two port and any p port SRAMs are presented together with some preliminary test results showing the importance of the new tests in reducing DPM level The impact of the port restrictions e g read only ports on the fault models tests and test strategies is also discussed Features Fault primitive based analysis of memory faults A complete framework of and classification memory faults A systematic way to develop optimal and high quality memory test algorithms A systematic way to develop test patterns for any multi port SRAM Challenges and trends in embedded memory testing Advances in Electronic Testing Dimitris Gizopoulos, 2006-01-22 Advances in Electronic Testing Challenges and Methodologies is a new type of edited volume in the Frontiers in Electronic Testing book series devoted to recent advances in electronic circuits testing The book is a comprehensive elaboration on important topics which capture major research and development efforts today The motivation and inspiration behind this book is to deliver a thorough text that focuses on the evolution of test technology provides insight about the abiding importance of discussed topics records today's state of the art and industrial practices and trends reveals the challenges for emerging testing methodologies and envisages the future of this journey The book consists of eleven edited chapters written by experts in Defect Oriented Testing Nanometer Technologies Failures and Testing Silicon Debug Delay Testing High Speed Test Interfaces DFT Oriented Low Cost Testers Embedded Cores and System on Chip Testing Memory Testing Mixed Signal Testing RF Testing and Loaded Board Testing Contributing authors are affiliated with in alphabetical order Agilent ARM Balearic Islands Univ IBM Inovys Intel Logic Vision Magma Mentor Graphics New Mexico Univ Sandia National Labs Synopsys Teradyne and Texas Instruments Advances in Electronic Testing Challenges and Methodologies is an advanced textbook and reference point for senior undergraduate and graduate students in MSc or PhD tracks professors and research leaders in the electronic testing domain It is also for industry design and test engineers and managers seeking a global view and understanding of test technology practices and methodologies and a dense elaboration on test related issues they face in their development projects There is a definite need for documenting the advances in testing I find the work of this edited volume by Dimitris Gizopoulos and his team of authors to be significant and timely the book provides besides novel test methodologies a collective insight into the emerging aspects of testing This I think is beneficial to practicing engineers and researchers both of whom must stay at the forefront of technology This latest addition to the Frontiers Series is destined to serve an important role From the Foreword by Vishwani D Agrawal Consulting Editor Frontiers in Electronic Testing Book Series High <u>Performance Memory Testing</u> R. Dean Adams, 2005-12-29 Are memory applications more critical than they have been in the past Yes but even more critical is the number of designs and the sheer number of bits on each design It is assured that catastrophes which were avoided in the past because memories were small will easily occur if the design and test engineers

do not do their jobs very carefully High Performance Memory Testing Design Principles Fault Modeling and Self Test is based on the author s 20 years of experience in memory design memory reliability development and memory self test High Performance Memory Testing Design Principles Fault Modeling and Self Test is written for the professional and the researcher to help them understand the memories that are being tested

Unveiling the Magic of Words: A Review of "Test Resource Partitioning For Systemonachip"

In some sort of defined by information and interconnectivity, the enchanting power of words has acquired unparalleled significance. Their capability to kindle emotions, provoke contemplation, and ignite transformative change is really awe-inspiring. Enter the realm of "**Test Resource Partitioning For Systemonachip**," a mesmerizing literary masterpiece penned by way of a distinguished author, guiding readers on a profound journey to unravel the secrets and potential hidden within every word. In this critique, we shall delve in to the book is central themes, examine its distinctive writing style, and assess its profound impact on the souls of its readers.

https://archive.kdd.org/data/scholarship/index.jsp/Suffering%20And%20Illness%20Insights%20For%20Caregivers.pdf

# **Table of Contents Test Resource Partitioning For Systemonachip**

- 1. Understanding the eBook Test Resource Partitioning For Systemonachip

- The Rise of Digital Reading Test Resource Partitioning For Systemonachip

- Advantages of eBooks Over Traditional Books

- 2. Identifying Test Resource Partitioning For Systemonachip

- Exploring Different Genres

- Considering Fiction vs. Non-Fiction

- Determining Your Reading Goals

- 3. Choosing the Right eBook Platform

- Popular eBook Platforms

- Features to Look for in an Test Resource Partitioning For Systemonachip

- User-Friendly Interface

- 4. Exploring eBook Recommendations from Test Resource Partitioning For Systemonachip

- Personalized Recommendations

- Test Resource Partitioning For Systemonachip User Reviews and Ratings

- Test Resource Partitioning For Systemonachip and Bestseller Lists

- 5. Accessing Test Resource Partitioning For Systemonachip Free and Paid eBooks

- Test Resource Partitioning For Systemonachip Public Domain eBooks

- Test Resource Partitioning For Systemonachip eBook Subscription Services

- Test Resource Partitioning For Systemonachip Budget-Friendly Options

- 6. Navigating Test Resource Partitioning For Systemonachip eBook Formats

- o ePub, PDF, MOBI, and More

- Test Resource Partitioning For Systemonachip Compatibility with Devices

- Test Resource Partitioning For Systemonachip Enhanced eBook Features

- 7. Enhancing Your Reading Experience

- Adjustable Fonts and Text Sizes of Test Resource Partitioning For Systemonachip

- Highlighting and Note-Taking Test Resource Partitioning For Systemonachip

- Interactive Elements Test Resource Partitioning For Systemonachip

- 8. Staying Engaged with Test Resource Partitioning For Systemonachip

- Joining Online Reading Communities

- Participating in Virtual Book Clubs

- Following Authors and Publishers Test Resource Partitioning For Systemonachip

- 9. Balancing eBooks and Physical Books Test Resource Partitioning For Systemonachip

- Benefits of a Digital Library

- Creating a Diverse Reading Collection Test Resource Partitioning For Systemonachip

- 10. Overcoming Reading Challenges

- Dealing with Digital Eye Strain

- Minimizing Distractions

- Managing Screen Time

- 11. Cultivating a Reading Routine Test Resource Partitioning For Systemonachip

- Setting Reading Goals Test Resource Partitioning For Systemonachip

- Carving Out Dedicated Reading Time

- 12. Sourcing Reliable Information of Test Resource Partitioning For Systemonachip

- Fact-Checking eBook Content of Test Resource Partitioning For Systemonachip

- Distinguishing Credible Sources

- 13. Promoting Lifelong Learning

- Utilizing eBooks for Skill Development

- Exploring Educational eBooks

- 14. Embracing eBook Trends

- Integration of Multimedia Elements

- Interactive and Gamified eBooks

#### **Test Resource Partitioning For Systemonachip Introduction**

In todays digital age, the availability of Test Resource Partitioning For Systemonachip books and manuals for download has revolutionized the way we access information. Gone are the days of physically flipping through pages and carrying heavy textbooks or manuals. With just a few clicks, we can now access a wealth of knowledge from the comfort of our own homes or on the go. This article will explore the advantages of Test Resource Partitioning For Systemonachip books and manuals for download, along with some popular platforms that offer these resources. One of the significant advantages of Test Resource Partitioning For Systemonachip books and manuals for download is the cost-saving aspect. Traditional books and manuals can be costly, especially if you need to purchase several of them for educational or professional purposes. By accessing Test Resource Partitioning For Systemonachip versions, you eliminate the need to spend money on physical copies. This not only saves you money but also reduces the environmental impact associated with book production and transportation. Furthermore, Test Resource Partitioning For Systemonachip books and manuals for download are incredibly convenient. With just a computer or smartphone and an internet connection, you can access a vast library of resources on any subject imaginable. Whether youre a student looking for textbooks, a professional seeking industry-specific manuals, or someone interested in self-improvement, these digital resources provide an efficient and accessible means of acquiring knowledge. Moreover, PDF books and manuals offer a range of benefits compared to other digital formats. PDF files are designed to retain their formatting regardless of the device used to open them. This ensures that the content appears exactly as intended by the author, with no loss of formatting or missing graphics. Additionally, PDF files can be easily annotated, bookmarked, and searched for specific terms, making them highly practical for studying or referencing. When it comes to accessing Test Resource Partitioning For Systemonachip books and manuals, several platforms offer an extensive collection of resources. One such platform is Project Gutenberg, a nonprofit organization that provides over 60,000 free eBooks. These books are primarily in the public domain, meaning they can be freely distributed and downloaded. Project Gutenberg offers a wide range of classic literature, making it an excellent resource for literature enthusiasts. Another popular platform for Test Resource Partitioning For Systemonachip books and manuals is Open Library. Open Library is an initiative of the Internet Archive, a non-profit organization dedicated to digitizing cultural artifacts and making them accessible to the public. Open

Library hosts millions of books, including both public domain works and contemporary titles. It also allows users to borrow digital copies of certain books for a limited period, similar to a library lending system. Additionally, many universities and educational institutions have their own digital libraries that provide free access to PDF books and manuals. These libraries often offer academic texts, research papers, and technical manuals, making them invaluable resources for students and researchers. Some notable examples include MIT OpenCourseWare, which offers free access to course materials from the Massachusetts Institute of Technology, and the Digital Public Library of America, which provides a vast collection of digitized books and historical documents. In conclusion, Test Resource Partitioning For Systemonachip books and manuals for download have transformed the way we access information. They provide a cost-effective and convenient means of acquiring knowledge, offering the ability to access a vast library of resources at our fingertips. With platforms like Project Gutenberg, Open Library, and various digital libraries offered by educational institutions, we have access to an ever-expanding collection of books and manuals. Whether for educational, professional, or personal purposes, these digital resources serve as valuable tools for continuous learning and self-improvement. So why not take advantage of the vast world of Test Resource Partitioning For Systemonachip books and manuals for download and embark on your journey of knowledge?

#### **FAQs About Test Resource Partitioning For Systemonachip Books**

How do I know which eBook platform is the best for me? Finding the best eBook platform depends on your reading preferences and device compatibility. Research different platforms, read user reviews, and explore their features before making a choice. Are free eBooks of good quality? Yes, many reputable platforms offer high-quality free eBooks, including classics and public domain works. However, make sure to verify the source to ensure the eBook credibility. Can I read eBooks without an eReader? Absolutely! Most eBook platforms offer webbased readers or mobile apps that allow you to read eBooks on your computer, tablet, or smartphone. How do I avoid digital eye strain while reading eBooks? To prevent digital eye strain, take regular breaks, adjust the font size and background color, and ensure proper lighting while reading eBooks. What the advantage of interactive eBooks? Interactive eBooks incorporate multimedia elements, quizzes, and activities, enhancing the reader engagement and providing a more immersive learning experience. Test Resource Partitioning For Systemonachip is one of the best book in our library for free trial. We provide copy of Test Resource Partitioning For Systemonachip in digital format, so the resources that you find are reliable. There are also many Ebooks of related with Test Resource Partitioning For Systemonachip. Where to download Test Resource Partitioning For Systemonachip online for free? Are you looking for Test Resource Partitioning For Systemonachip for find then search around for online. Without a doubt there are numerous

these available and many of them have the freedom. However without doubt you receive whatever you purchase. An alternate way to get ideas is always to check another Test Resource Partitioning For Systemonachip. This method for see exactly what may be included and adopt these ideas to your book. This site will almost certainly help you save time and effort, money and stress. If you are looking for free books then you really should consider finding to assist you try this. Several of Test Resource Partitioning For Systemonachip are for sale to free while some are payable. If you arent sure if the books you would like to download works with for usage along with your computer, it is possible to download free trials. The free guides make it easy for someone to free access online library for download books to your device. You can get free download on free trial for lots of books categories. Our library is the biggest of these that have literally hundreds of thousands of different products categories represented. You will also see that there are specific sites catered to different product types or categories, brands or niches related with Test Resource Partitioning For Systemonachip. So depending on what exactly you are searching, you will be able to choose e books to suit your own need. Need to access completely for Campbell Biology Seventh Edition book? Access Ebook without any digging. And by having access to our ebook online or by storing it on your computer, you have convenient answers with Test Resource Partitioning For Systemonachip To get started finding Test Resource Partitioning For Systemonachip, you are right to find our website which has a comprehensive collection of books online. Our library is the biggest of these that have literally hundreds of thousands of different products represented. You will also see that there are specific sites catered to different categories or niches related with Test Resource Partitioning For Systemonachip So depending on what exactly you are searching, you will be able to choose ebook to suit your own need. Thank you for reading Test Resource Partitioning For Systemonachip. Maybe you have knowledge that, people have search numerous times for their favorite readings like this Test Resource Partitioning For Systemonachip, but end up in harmful downloads. Rather than reading a good book with a cup of coffee in the afternoon, instead they juggled with some harmful bugs inside their laptop. Test Resource Partitioning For Systemonachip is available in our book collection an online access to it is set as public so you can download it instantly. Our digital library spans in multiple locations, allowing you to get the most less latency time to download any of our books like this one. Merely said, Test Resource Partitioning For Systemonachip is universally compatible with any devices to read.

# **Find Test Resource Partitioning For Systemonachip:**

## suffering and illness insights for caregivers

subtle is the lord suddenly single a lifeline for anyone who has lost a love succeb strategies lifes simple truthbigned subaltern studies iii writings on south asian history and society

successful failures wisdom to inspire you

suffragettes international the world-wide campaign for womens rights

successful grandparenting the essential guide to one of lifes most rewarding relationships

subway series

#### subsidence due to fluid withdrawal

submarines the illustrated history

su doku 1 the utterly addictive number-placing puzzle

style of connectedness gravitys rainbow and thomas pynchon

stylish napkins 5minute ideas to transform your table

substance its nature and existence

# **Test Resource Partitioning For Systemonachip:**

https://dtnacontent-dtna.prd.freightliner.com/cont... Freightliner Century Wiring | PDF Fuse Box Diagram KIA Sportage (QL; 2017-2020 ... Have a 2006 freightliner Century. The fuse panel/power May 16, 2018 — The fuse panel/power distribution module has no labels on any of the fuses/breakers/relays. Need a diagram of fuse location/function. fuse block diagram? TruckersReport.com Trucking Forum Jul 11, 2013 — I have a friend that has a 2007 century. His fuses aren't marked by anything. Does anyone have or know where I can get a diagram so we can ... Freightliner Century (2004-2010) Installation Guide Nov 9, 2022 — Fuse Panel. The fuse panel is behind the glove box on the passenger side of the vehicle. Open up the glove compartment and remove the screws ... I need a fuse panel diagram for a 2005 Freightliner Columbia Mar 1, 2023 — I need a fuse panel diagram for a 2005 Freightliner Columbia 120 with a series 60 engine - Answered by a verified Technician. Century Class Maintenance Manual Perform the pretrip and post-trip inspections, and daily/weekly/monthly maintenance, as outlined in the vehicle driver's manual. Major components, such as ... Here is a photo of the fuse panel and layout for the argosy ... Here is a photo of the fuse panel and layout for the argosy 2005. Only posting as I had a hard time getting the info I needed. 09-12 freightliner fuse box cover diagram - YouTube Narrative Therapy Treatment Plan & Example Work with the client to define their goals for therapy. These goals should be specific, measurable, achievable, relevant, and time-bound (SMART). Develop ... Narrative Therapy Case Conceptualization: Treatment ... A narrative therapy treatment plan can treat depression and handle a crisis. In this case study template, you will discover an excellent narrative therapy case ... 19 Best Narrative Therapy Techniques & Worksheets [+PDF] In narrative therapy, the client aims to construct a storyline to their experiences that offers meaning, or gives them a positive and functional identity. This ... An Introduction to Narrative

Therapy by L DeKruyf · 2008 · Cited by 7 — Treatment Goals The objective of narrative therapy is not to find a "solution." Rather, it is to help clients reclaim the authority to author their own stories ... Narrative Therapy: Definition, Techniques & Interventions by OG Evans — Narrative therapy seeks to change a problematic narrative into a more productive or healthier one. This is often done by assigning the person ... Narrative Therapy Techniques (4 Examples) Oct 8, 2023 — Narrative therapy is an approach that aims to empower people. In this approach, patients tell their story as if they were the protagonist in a ... Narrative Therapy - Fisher Digital Publications by RH Rice · 2015 · Cited by 20 — Abstract. Narrative therapy (NT) is a strengths-based approach to psychotherapy that uses collaboration between the client or family and the therapist to ... Narrative Therapy Treatment - YouTube Case Conceptualization and Treatment Plan of Marvin ... Narrative theory hypothesizes that client distress arises from suffering causes by personal life stories or experiences that have caused a low sense of self. Working as a Field Engineer at Schlumberger: 137 Reviews The job itself is very stressful and includes very long hours a lot of the time. There's no work life balance. Pros. Field Engineer | Schlumberger The WEC Field Engineer - DD identifies opportunities to improve service delivery, implements standard work, and manage, risk during service delivery. Roles and ... Early Careers - Operations Field Engineer. Be involved in every phase of our business; Field Specialist. Turn technical expertise into transformative impact; Field Technical Analyst. SLB Cement Field Engineer Salaries The average salary for a Field Engineer - Cementing is \$81,856 per year in United States, which is 29% lower than the average SLB salary of \$115,567 per year ... Cementing Field Specialist | Schlumberger The purpose of the position is to execute the different cementing processes of both primary and remediation oil wells. A successful person in this position must ... SLB Cement Field Engineer Salaries in Midland The average salary for a Cement Field Engineer is \$69,532 per year in Midland, TX, which is 27% lower than the average SLB salary of \$96,015 per year for this ... How is it to be a Field Engineer in Schlumberger? Dec 5, 2012 — A Field Engineer in Schlumberger is like an adjustable wrench. He/she can be used to tighten any bolt as and when needed... Instead of getting ... My Schlumberger Career- Field Engineer - YouTube Schlumberger - Cementing : r/oilandgasworkers Greetings,. I've just recieved a job offer letter from Schlumberger in Cementing as Field Engineer Trainee. I'm aware of Schlumberger general ...